Необходимость логического анализатора как

помощника при отладке последовательных линий

связи, например, (I^2)C, 1-Wire и параллельных шин,

например, интерфейса распространённых

индикаторов DataVision, очевидна. Однако

профессиональные логические анализаторы,

например, выпускаемые под маркой Techtronics и Adgilent, не

по карману не только радиолюбителю-разработчику,

но даже и не очень крупным фирмам. Применение же

аналогового осциллографа ограничивается тем,

что для наблюдения необходимо зацикливать

посылку команды, что не всегда приводит к

устойчивой картинке, особенно если в

микроконтроллере для каких-то других нужд

используется аппаратное прирывание, что

приводит к неодинаковости времени между

посылками и, как следствие, дрожанию картинки. В

то же время, учитывая распространённость ПЛИС,

изготовление простого анализатора для отладки

не слишком скоростных шин представляется весьма

реальным.

Предложенный анализатор имеет 16 входных каналов,

первые 8 из которых используются для задания

события, по которому сработает триггер записи в

память, и статическую память на 32К 16-разрядных

слов. Время выборки сигналов определяется

быстродействием ПЛИС и памяти; к примеру, Altera со

speedgrade 10 при проведении временного анализа

программой Max+II показала частоту 55 МГц, что

соответсвует времени выборки (с запасом) в 25МГц

(контроллер статической памяти расходует два

такта на запись в память). Возможен упрощённый

вариант, который можно видеть на расположенной

ниже фотографии, при котором ПЛИС тактируются

частотой, снимаемой с выхода XTAL2

микроконтроллера - этот вариант использовался в

виду того, что память со временем доступа 70нс не

позволяла реализовать максимально возможную

скорость. При использовании более

высокоскоростной памяти на плату

устанавливается кварцевый генератор

соответсвующей частоты. Анализатор соединяется

с ЭВМ по интерфейсу RS-232C, передавая данные для

отображения на экране. Команды и операции

передаются от ЭВМ по тому же интерфейсу.

2. Описание аппаратной части анализатора

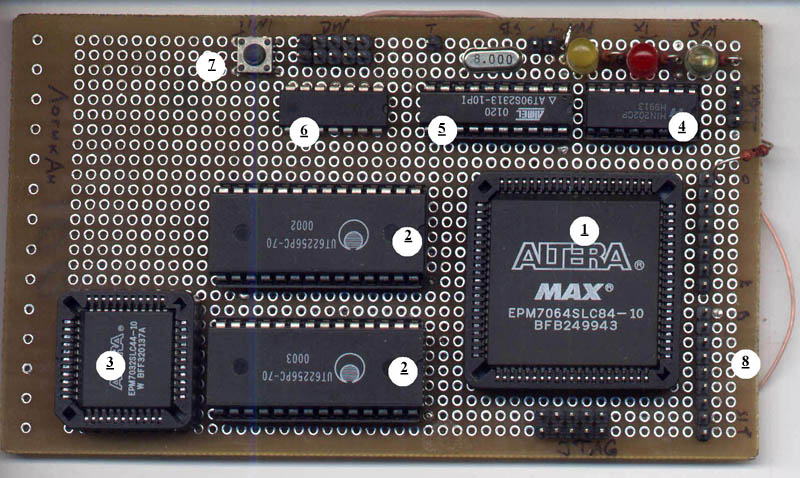

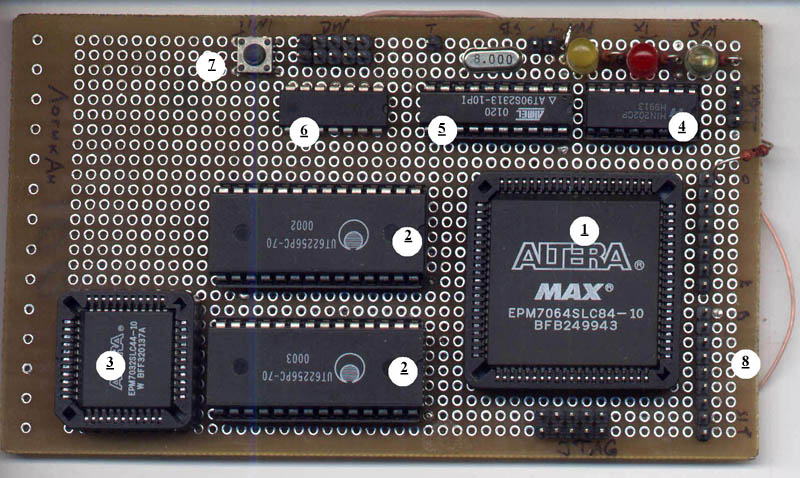

Рис. 1 Макетная отладочная плата анализатора

Макетная плата анализатора представлена на рисунке 1. Цифрами на рисунке обозначены: 1 - контроллер последовательности сигналов на микросхеме EPM7064 , 2 - статическая память 32Кх8 UT62256, 3 - контроллер статической памяти на микросхеме EPM7032, 4 - преобразователь уровней TTL-RS232C HIN202, 5 - микроконтроллер AT90S2313, 6 - формирователь фронтов тактовой частоты на инверторе 7404, 7 - кнопка запуска анализатора, 8 - колодка для подключения исследуемых сигналов. Применение микроконтроллера было продиктовано наличием в нём универсального асинхронного приёмопередатчика, позволяющего осуществлять связь с компьютером. Тактируется микроконтроллер от кварца частотой 8 МГц. С контроллером последоватльностей микроконтроллер (МК) связан двунаправленной восьмиразрядной шиной, позволяющей записывать конфигурационные регистры контроллера последовательностей и считывать его стотояние. Контроллер последовательностей (КП) осуществляет анализ входных данных и в зависимости от конфигурации выдаёт те или иные управляющие последовательности на контроллер памяти (КСП). Также КП каждый такт защёлкивает входные сигналы, направляя их на шину данных памяти. Команды и адрес на память подаются с КСП. КСП реализован отдельной микросхемой как по причине нехватки свободных выводов и места в микросхемы EPM7064, так и тем, что память может быть заменена на другую, с иными временными диаграммами, таким образом, КП не требовал бы заново отладки. Для индикации режима работы на плате предусмотрены три светодиода: жёлтый показывает, что питание на плату подано, красный - что идёт передача данных в ЭВМ, зелёный показывает, что анализатор либо ждёт прихода комбинации заданных сигналов, либо занят передачей данных. Кнопка 7 позволяет после загрузки конфигурационных регистров запустить анализатор на ожидание. Если управляющая комбинация не изменилась, то для повторного запуска достаточно снова нажать кнопку, не перезагружая регистры заново.

3. Работа с программной частью анализатора

Рис 2. Основное окно программы

На рисунке 2 показано основное окно программы работы с логическим анализатором. Программа была написана на Borland C++Builder и оттестирована под ОС WinXP. Замеченный недостаток при работе с данной ОС - медленное выполнение функций API, то есть от момента нажатия кпопки до пересылки данных в порт проходит ощутимое время. На окне программы расположены: слева - кнопки управления анализатором, внизу - радиокнопки задания условия срабатывания анализатора и кнопки управления маркерами. На окне диаграмм отображаются 16 линий и составленная из этих линий шина. Названия линий можно изменять в окне настроек, жёлтым подсвечивается та линия, по которой осуществляется поиск перепада. Каждой из восьми первых линий соответсвуют три радиокнопки: высокий уровень, безразлично и низкий уровень. Кнопки объеденяются по "И", то есть если задан высокий уровень на 5-м канале и низкий на первом, анализатор сработает по условию "канал-5 в высоком уровне И канал-1 в низком". Сигналы на остальных линиях будут игнорироваться КП при анализе условия срабатывания. При комбинации радиокнопок, показанной на рис.2, анализатор сработает при наличии низкого уровня на 0-м канале вне зависимости от того, в каком состоянии находятся остальные линии. Кнопка "Запуск" инициирует передачу конфинурирующей последовательности в анализатор. Анализатор может работать в двух режимах: непреывного записывания и ожидания. Режим ожидания включается выбором квадратика "Ждать" под кнопкой запуска перед нажатием этой кнопки. Режим ожидания означает то, что по срабатывании триггера условия КП запускает КСП, происходит запись в память и после этого анализатор останавливается до принятия следующей команды. Режим непрерывной развёртки означает, что запись в память происходит постоянно после нажатия кнопки 7 на плате анализатора, по срабатывании же триггера память дозаписывается до конца и анализатор останавливается. Кнопка "Прервать" служит для выхода из режима ожидания последовательности (при этом на плате гаснет зелёный светодиод). Кнопка "Считать" инициирует передачу данных в ЭВМ и отображение их на временной диаграмме.

Рис 3. Окно настроек

В окно настроек можно попасть либо нажатием иконки с молоточком, либо через меню Вид/Настройка. В этом окне можно изменить цвет диаграмм, выбрать порт, с которым работает анализатор, и указать используемую частоту дискретизации для правильного отображения временных отметок и измерения временных интервалов на окне диаграмм. Для переименования названия линии выберите её среди линий списка "Названия линий", введите новое название и нажмите клавишу "Enter". Список автоматически перейдёт на следующую линию, новое же название будет сохранено и отобразится после нажатия кнопки "ОК".

Рис. 4. Поиск перепадов.

Временную диаграмму можно сохранить на диск и потом просмотреть либо через меню "Файл", либо нажатием соответсвующей иконки. Диаграмма сохранится на диске файлом с расширением *.lan. Для измерения временних интервалов предназначены два маркера. Первый перемещается щёлканьем левой клавиши либо перемещением мыши с нажатой левой клавишей по соответствующему месту диаграммы. Аналогично второй маркер связян с правой клавишей мыши. Внизу показазывается точное положение маркера. Временные метки на диаграмме для уменьшения загромождения имеют длину в четыре символа, поэтому ориентироваться следует на указанную внизу под словами "Отсчёт №" величину. На рис. 4 показан пример округления величины, указанной на временной метке. Если на диаграмме присутствуют оба маркера, то дополнительно отображается разность между маркерами. Диаграмму при этом для удобства можно укрупнить, либо уменьшить, нажав соответствующие иконки. Для поиска следующего перепада следует сперва выделить сигнал на диаграмме, щёлкнув на нём правой клавишей мыши (название сигнала подсветится жёлтым и появится маркер), а затем выбрать, в какую сторону от маркера следует искать перепад. Выбор осуществляется либо нажатием сответсвующей иконки (рис. 4), либо через меню "Вид", либо стрелками курсора "Влево" или "Вправо", удерживая нажатой клавишу "Alt".

Здесь находится архив в формате ZIP размером 360 Кб, в котором хранятся следующие файлы:

Файлы logic_a.v и sram_cnt.v представляют собой описание КП и КСП на языке Verilog, файлы с тем же названием, но расширением *.pof являются файлами прошивки Altera. Файлы logican.h и logican.c являются заголовочным и программный файлами для IAR EW, это программа работы микроконтроллера. logican.hex - откомпилированный файл для загрузки микроконтроллера в формате Intel HEX. Файл schLA.gif - графический файл с изображением схемы, LogicAn.sch - схема в формате программы ACCEL EDA - для повышения разборчивости. И файл WaveFormViewer.exe - программа, работа которой пояснялась в п.3.

Автор проекта: Александр Корниленко

(E-mail: seagull@mail.ru)